#

# **VIPA System 300S**

**SPEED7 - SM | Manual** HB140E\_SM | Rev. 09/45

November 2009

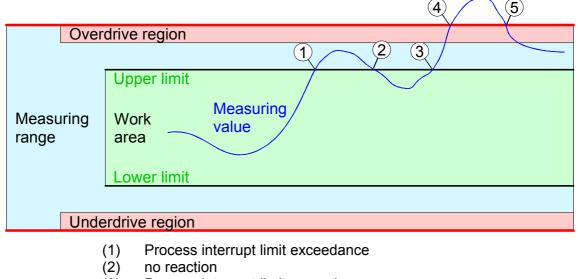

### Copyright © VIPA GmbH. All Rights Reserved.

This document contains proprietary information of VIPA and is not to be disclosed or used except in accordance with applicable agreements.

This material is protected by the copyright laws. It may not be reproduced, distributed, or altered in any fashion by any entity (either internal or external to VIPA), except in accordance with applicable agreements, contracts or licensing, without the express written consent of VIPA and the business management owner of the material.

For permission to reproduce or distribute, please contact: VIPA, Gesellschaft für Visualisierung und Prozessautomatisierung mbH Ohmstraße 4, D-91074 Herzogenaurach,Germany Tel.: +49 (91 32) 744 -0 Fax.: +49 9132 744 1864 EMail: info@vipa.de http://www.vipa.de

### Note

Every effort has been made to ensure that the information contained in this document was complete and accurate at the time of publishing. Nevertheless, the authors retain the right to modify the information. This customer document describes all the hardware units and functions known at the present time. Descriptions may be included for units which are not present at the customer site. The exact scope of delivery is described in the respective purchase contract.

### **CE Conformity**

Hereby, VIPA GmbH declares that the products and systems are in compliance with the essential requirements and other relevant provisions of the following directives:

- 2004/108/EC Electromagnetic Compatibility Directive

- 2006/95/EC Low Voltage Directive

Conformity is indicated by the CE marking affixed to the product.

### **Conformity Information**

For more information regarding CE marking and Declaration of Conformity (DoC), please contact your local VIPA customer service organization.

### Trademarks

VIPA, SLIO, System 100V, System 200V, System 300V, System 300S, System 400V, System 500S and Commander Compact are registered trademarks of VIPA Gesellschaft für Visualisierung und Prozessautomatisierung mbH.

SPEED7 is a registered trademark of profichip GmbH.

SIMATIC, STEP, SINEC, S7-300 and S7-400 are registered trademarks of Siemens AG.

Microsoft und Windows are registered trademarks of Microsoft Inc., USA.

Portable Document Format (PDF) and Postscript are registered trademarks of Adobe Systems, Inc.

All other trademarks, logos and service or product marks specified herein are owned by their respective companies.

### Information product support

Contact your local VIPA Customer Service Organization representative if you wish to report errors or questions regarding the contents of this document. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telefax:+49 9132 744 1204 EMail: documentation@vipa.de

### **Technical support**

Contact your local VIPA Customer Service Organization representative if you encounter problems with the product or have questions regarding the product. If you are unable to locate a customer service center, contact VIPA as follows:

VIPA GmbH, Ohmstraße 4, 91074 Herzogenaurach, Germany

Telephone: +49 9132 744 1150/1180 (Hotline) EMail: support@vipa.de

# Contents

| About this manual                              | 1    |

|------------------------------------------------|------|

| Safety information                             |      |

| Chapter 1 Basics                               | 1-1  |

| Safety Information for Users                   |      |

| General description of the System 300          | 1-3  |

| System 300S                                    |      |

| Chapter 2 Assembly and installation guidelines | 2-1  |

| Overview                                       | 2-2  |

| Installation dimensions                        | 2-3  |

| Installation Standard-Bus                      | 2-4  |

| Assembly SPEED-Bus                             | 2-5  |

| Cabling                                        | 2-8  |

| Installation Guidelines                        | 2-12 |

| Chapter 3 Digital I/O modules FAST - SPEED-Bus |      |

| System overview                                |      |

| Security hint for DIO modules                  |      |

| Addressing at SPEED-Bus                        |      |

| Project engineering                            |      |

| 321-1BH70 - DI 16xDC 24V                       |      |

| 322-1BH70 - DO 16xDC 24V 0.5A                  |      |

| 323-1BH70 - DIO 16xDC 24V 0.5A                 |      |

| Chapter 4 Analog I/O modules FAST - SPEED-Bus  |      |

| System overview                                |      |

| Security hint                                  |      |

| General                                        |      |

| Analog value representation                    |      |

| Operating modes                                |      |

| Addressing at SPEED-Bus                        |      |

| Project engineering                            |      |

| Parameterization                               |      |

| SFC 193 - Oscilloscope-/FIFO function          |      |

| Example for the oscilloscope function          |      |

| Example for the FIFO function                  |      |

| Diagnostics                                    |      |

| 331-7xF70 - AI 8x16Bit                         |      |

| Appendix                                       | A-1  |

| Index                                          | A-1  |

# About this manual

This manual describes the System 300S SPEED7 signal modules (SM) for SPEED-Bus. Here you may find besides of a product overview a detailed description of the single modules. You'll receive information about the connection and the deployment of the System 300S SM modules.

### Overview Chapter 1: Principles

This chapter introduces the System 300 from VIPA as central res. decentral automation system.

### Chapter 2: Hardware description

The SPEED7 CPU is available in different variants. This chapter describes the hardware of the different versions.

# Chapter 3: Digital I/O modules FAST - SPEED-Bus

This chapter describes the fast digital I/O modules for the SPEED-Bus.

### Chapter 4: Analog I/O modules FAST - SPEED-Bus

This chapter describes the fast analog I/O modules for the SPEED-Bus.

| Objective and contents   | This manual describes the <b>s</b> ignal <b>m</b> odules (SM) for SPEED-Bus of the System 300S from VIPA. It contains a description of the construction, project engineering and usage.                                                     |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target audience          | The manual is targeted at users who have a background in automation technology.                                                                                                                                                             |

| Structure of the manual  | The manual consists of chapters. Every chapter provides a self-contained description of a specific topic.                                                                                                                                   |

| Guide to the<br>document | <ul> <li>The following guides are available in the manual:</li> <li>an overall table of contents at the beginning of the manual</li> <li>an overview of the topics for every chapter</li> <li>an index at the end of the manual.</li> </ul> |

| Availability             | <ul> <li>The manual is available in:</li> <li>printed form, on paper</li> <li>in electronic form as PDF-file (Adobe Acrobat Reader)</li> </ul>                                                                                              |

| lcons<br>Headings        | Important passages in the text are highlighted by following icons and headings:                                                                                                                                                             |

| $\underline{\wedge}$     | <b>Danger!</b><br>Immediate or likely danger.<br>Personal injury is possible.                                                                                                                                                               |

| $\underline{\wedge}$     | Attention!<br>Damages to property is likely if these warnings are not heeded.                                                                                                                                                               |

|                          | <b>Note!</b><br>Supplementary information and useful tips.                                                                                                                                                                                  |

# **Safety information**

Applications conforming with specifications The SPEED7 signal modules are constructed and produced for:

- for the deployment with VIPA SPEED-Bus

- communication and process control

- general control and automation applications

- industrial applications

- operation within the environmental conditions specified in the technical data

- installation into a cubicle

### Danger!

This device is not certified for applications in

• in explosive environments (EX-zone)

Documentation

The manual must be available to all personnel in the

- project design department

- installation department

- commissioning

- operation

# The following conditions must be met before using or commissioning the components described in this manual:

- Modification to the process control system should only be carried out when the system has been disconnected from power!

- Installation and modifications only by properly trained personnel

- The national rules and regulations of the respective country must be satisfied (installation, safety, EMC ...)

Disposal

National rules and regulations apply to the disposal of the unit!

# Chapter 1 Basics

OverviewThis Basics contain hints for the usage and information about a SPEED7<br/>system from VIPA.General information about the System 300S like dimensions and<br/>environment conditions will also be found.

| Content | Торіс                                 | Page |

|---------|---------------------------------------|------|

|         | Chapter 1 Basics                      | 1-1  |

|         | Safety Information for Users          | 1-2  |

|         | General description of the System 300 | 1-3  |

|         | System 300S                           | 1-4  |

# Safety Information for Users

Handling of electrostatic sensitive modules VIPA modules make use of highly integrated components in MOS-Technology. These components are extremely sensitive to over-voltages that can occur during electrostatic discharges.

The following symbol is attached to modules that can be destroyed by electrostatic discharges.

The Symbol is located on the module, the module rack or on packing material and it indicates the presence of electrostatic sensitive equipment.

It is possible that electrostatic sensitive equipment is destroyed by energies and voltages that are far less than the human threshold of perception. These voltages can occur where persons do not discharge themselves before handling electrostatic sensitive modules and they can damage components thereby, causing the module to become inoperable or unusable.

Modules that have been damaged by electrostatic discharges can fail after a temperature change, mechanical shock or changes in the electrical load.

Only the consequent implementation of protection devices and meticulous attention to the applicable rules and regulations for handling the respective equipment can prevent failures of electrostatic sensitive modules.

Modules must be shipped in the original packing material.

modules Measurements and

sensitive modules

alterations on

electrostatic

Shipping of

When you are conducting measurements on electrostatic sensitive modules you should take the following precautions:

- Floating instruments must be discharged before use.

- Instruments must be grounded.

Modifying electrostatic sensitive modules you should only use soldering irons with grounded tips.

### Attention!

Personnel and instruments should be grounded when working on electrostatic sensitive modules.

System 300S

# **General description of the System 300**

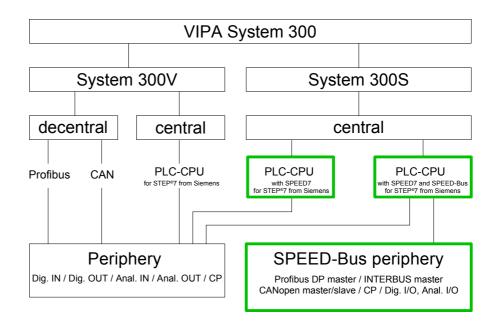

The System 300The System 300 is a modular automation system for middle and high<br/>performance needs, which may be used, either centralized or<br/>decentralized. The single modules are directly clipped to the profile rail and<br/>are connected together with the help of bus clips at the backside.<br/>The CPUs of the System 300 are instruction set compatible to S7-300 from<br/>Siemens.

**System 300V** VIPA differentiates between System 300V and System 300S.

System 300V

The System 300V allows you to resolve automation tasks centralized and decentralized. The single modules of the System 300V from VIPA are similar in construction to Siemens. Due to the compatible backplane bus, the modules from VIPA and Siemens can be mixed.

• System 300S

The System 300S extends the central area with high-speed CPUs that have the integrated SPEED7 chip. Additionally some CPU's have got a parallel SPEED-Bus that allows the modular connection of fast peripheral modules like IOs or bus master.

# System 300S

**Overview**

The CPUs 31xS are based upon the SPEED7 technology. This supports the CPU at programming and communication by means of co-processors that causes a power improvement for highest needs.

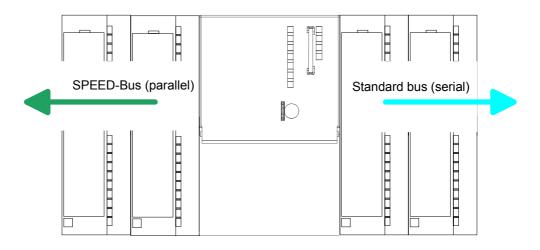

Except of the basic variant, all SPEED7-CPUs are provided with a parallel SPEED-Bus that enables the additional connection of up to 10 modules from the SPEED-Bus periphery. While the standard peripheral modules are plugged-in at the right side of the CPU, the SPEED bus peripheral modules are connected via a SPEED-Bus bus connector at the left side of the CPU.

**CPU 31xS** The System 300S series consists of a number of CPUs. These are programmed in STEP<sup>®</sup>7 from Siemens. For this you may use WinPLC7 from VIPA or the Siemens SIMATIC manager.

CPUs with integrated Ethernet interfaces or additional serial interfaces simplify the integration of the CPU into an existing network or the connection of additional peripheral equipment.

The user application is stored in the battery buffered RAM or on an additionally pluggable MMC storage module.

Due to the automatic address allocation, the deployment of the CPUs 31xS allows to address 32 peripheral modules.

Additionally some SPEED7-CPUs have got a parallel SPEED-Bus that allows the modular connection of fast peripheral modules like IOs or bus master.

| SPEED-Bus                           | The SPEED-Bus is a 32Bit parallel bus developed from VIPA with a maximum data rate of 40MByte/s. Via the SPEED-Bus you may connect up to 10 SPEED-Bus modules to your CPU 31xS.                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | In opposite to the "standard" backplane bus where the modules are plugged-in at the right side of the CPU by means of single bus connectors, the modules at the SPEED-Bus are plugged-in at the left side of the CPU via a special SPEED-Bus rail. |

|                                     | VIPA delivers profile rails with integrated SPEED-Bus for 2, 6 or 10 SPEED-Bus peripheral modules with different lengths.                                                                                                                          |

| SPEED-Bus<br>peripheral<br>modules  | The SPEED-Bus peripheral modules may exclusively plugged at the SPEED-Bus slots at the left side of the CPU. The following SPEED-Bus modules are in preparation:                                                                                   |

|                                     | • Fast field bus modules like Profibus DP, Interbus, CANopen master and CANopen slave                                                                                                                                                              |

|                                     | • Fast CP 343 (CP 343 Communication processor for Ethernet)                                                                                                                                                                                        |

|                                     | Fast CP 341 with double RS 422/485 interface                                                                                                                                                                                                       |

|                                     | <ul> <li>Fast digital input-/output modules (Fast Digital IN/OUT)</li> </ul>                                                                                                                                                                       |

| Memory<br>management                | Every CPU 31xS has an integrated work memory. During program run the total memory is divided into 50% for program code and 50% for data.                                                                                                           |

|                                     | Starting with CPU firmware 3.0.0 there is the possibility to extend the total memory to its maximum by means of a MCC memory extension card.                                                                                                       |

| Integrated<br>Profibus<br>DP master | The CPUs of the System 300S series with SPEED-Bus have an integrated Profibus DP master. Via the DP master with a data range of 1kByte for in-<br>and output you may address up to 125 DP slaves.                                                  |

|                                     | The project engineering takes place in WinPLC7 from VIPA or in the hardware configurator from Siemens.                                                                                                                                             |

| Integrated                          | Every CPU 31xS has an Ethernet interface for PG/OP communication. Via                                                                                                                                                                              |

| Ethernet PG/OP<br>channel           | the "PLC" functions you may directly access the Ethernet PG/OP channel<br>and program res. remote control your CPU. A max. of 4 PG/OP<br>connections is available.                                                                                 |

|                                     | You may also access the CPU with a visualization software via these connections.                                                                                                                                                                   |

| Operation Security          | <ul> <li>Wiring by means of spring pressure connections (CageClamps) at the front connector</li> <li>Core cross-section 0.082.5mm<sup>2</sup></li> <li>Total isolation of the wiring at module change</li> <li>Potential separation of all modules to the backplane bus</li> <li>ESD/Burst acc. IEC 61000-4-2/IEC 61000-4-4 (up to level 3)</li> <li>Shock resistance acc. IEC 60068-2-6 / IEC 60068-2-27 (1G/12G)</li> </ul>                                                                                                                                                                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental<br>conditions | <ul> <li>Operating temperature: 0 +60°C</li> <li>Storage temperature: -25 +70°C</li> <li>Relative humidity: 5 95% without condensation</li> <li>Ventilation by means of a fan is not required</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

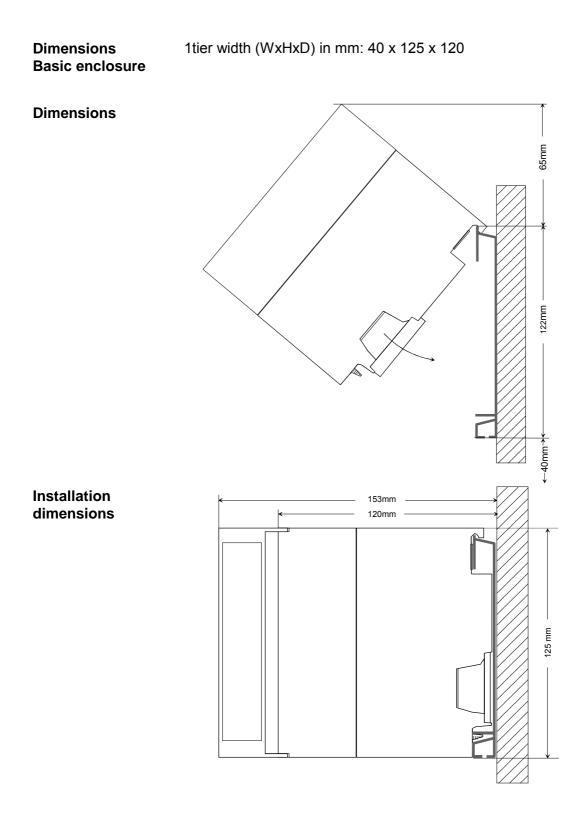

| Dimensions/<br>Weight       | <ul> <li>Available lengths of the profile rail in mm: 160, 482, 530, 830 and 2000</li> <li>Dimensions of the basic enclosure:<br/>1tier width: (HxWxD) in mm: 40x125x120<br/>2tier width: (HxWxD) in mm: 80x125x120</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Compatibility               | Modules and CPUs of the System 300 from VIPA and Siemens may be<br>used at the "Standard" bus as a mixed configuration.<br>The project engineering takes place in WinPLC7 from VIPA or in the<br>hardware configurator from Siemens.<br>The SPEED7 CPUs from VIPA are instruction compatible to the<br>programming language STEP <sup>®</sup> 7 from Siemens and may be programmed<br>via WinPLC7 from VIPA or via the Siemens SIMATIC manager.<br>Here the instruction set of the S7-400 from Siemens is used.                                                                                                                                    |

|                             | <b>Note!</b><br>Please do always use the <b>CPU 318-2DP (6ES7 318-2AJ00-0AB0/V3.0)</b><br>from Siemens of the hardware catalog to project a SPEED7-CPU with<br>SPEED-Bus from VIPA. For the project engineering, a thorough<br>knowledge of the Siemens SIMATIC manager and the hardware<br>configurator from Siemens is required!                                                                                                                                                                                                                                                                                                                 |

| Integrated<br>power supply  | Every CPU res. bus coupler comes with an integrated power supply. The power supply has to be supplied with DC 24V. By means of the supply voltage, the bus coupler electronic is supplied as well as the connected modules via backplane bus. Please regard that the integrated power supply may supply the backplane bus the backplane bus (SPEED-Bus and Standard-Bus) depending on the CPU with a sum with max. 5A. The power supply is protected against inverse polarity and overcurrent. Every SPEED-Bus rail has a plug-in option for an external power supply. This allows you to raise the maximum current at the backplane bus for 5.5A. |

# Chapter 2 Assembly and installation guidelines

**Overview** In this chapter you will find all information, required for the installation and the cabling of a process control with the components of the System 300.

###

# Overview

**General** While the standard peripheral modules are plugged-in at the right side of the CPU, the SPEED-Bus peripheral modules are connected via a SPEED-Bus bus connector at the left side of the CPU.

VIPA delivers profile rails with integrated SPEED-Bus for 2, 6 or 10 SPEED-Bus peripheral modules with different lengths.

SerialThe single modules are directly installed on a profile rail and connected viaStandard busThe backplane bus coupler. Before installing the modules you have to clip<br/>the backplane bus coupler to the module from the backside.<br/>The backplane bus coupler is included in the delivery of the peripheral<br/>modules.

ParallelWith SPEED-Bus the bus connection happens via a SPEED-Bus railSPEED-Busintegrated in the profile rail at the left side of the CPU. Due to the parallel<br/>SPEED-Bus not all slots must be occupied in sequence.

SLOT 1 for additional At SLOT 1 DCDC) you may plug either a SPEED-Bus module or an additional power supply.

You may assemble the System 300 horizontally, vertically or lying.

Assembly possibilities

| verti<br>asser |  |

|----------------|--|

| 0              |  |

Please regard the allowed environment temperatures:

- horizontal assembly: from 0 to 60°C

- vertical assembly: from 0 to 40°C

- lying assembly: from 0 to 40°C

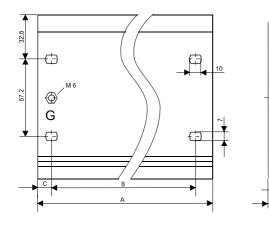

# Installation dimensions

# **Installation Standard-Bus**

### Approach

If you do not deploy SPEED-Bus modules, the assembly at the standard bus happens at the right side of the CPU with the following approach:

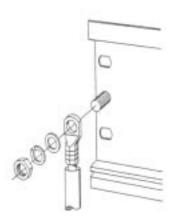

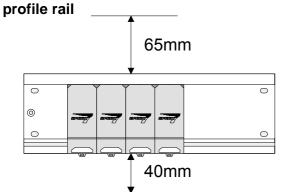

- Bolt the profile rail with the background (screw size: M6), so that you still have minimum 65mm space above and 40mm below the profile rail.

- If the background is a grounded metal or device plate, please look for a low-impedance connection between profile rail and background.

- Connect the profile rail with the protected earth conductor. For this purpose there is a bolt with M6-thread.

- The minimum cross-section of the cable to the protected earth conductor has to be 10mm<sup>2</sup>.

- Stick the power supply to the profile rail and pull it to the left side up to 5mm to the grounding bolt of the profile rail.

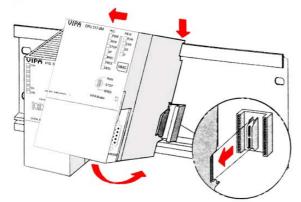

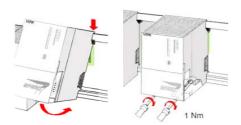

- Take a bus coupler and click it at the CPU from behind like shown in the picture.

- Stick the CPU to the profile rail right from the power supply and pull it to the power supply.

- Click the CPU downwards and bolt it like shown.

- Repeat this procedure with the peripheral modules, by clicking a backplane bus coupler, stick the module right from the modules you've already fixed, click it downwards and connect it with the backplane bus coupler of the last module and bolt it.

# Danger!

- Before installing or overhauling the system, the power supplies must be disconnected from voltage (pull the plug or remove the fuse)!

- Installation and modifications only by properly trained personnel!

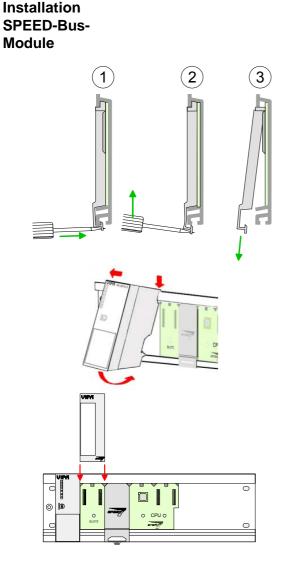

# **Assembly SPEED-Bus**

### Pre-manufactured SPEED-Bus profile rail

For the deployment of SPEED-Bus modules, a pre-manufactured SPEED-Bus rail is required. This is available mounted on a profile rail with 2, 6 or 10 extension plug-in locations.

# Installation of the

- Bolt the profile rail with the background (screw size: M6), so that you still have minimum 65mm space above and 40mm below the profile rail.

- Please look for a low-impedance connection between profile rail and background

Connect the profile rail with the protected earth conductor.

The minimum cross-section of the cable to the protected earth conductor has to be  $10 \text{mm}^2$ .

# **Profile rail**

| Order number    | SPEED-    | A      | В     | С     |

|-----------------|-----------|--------|-------|-------|

|                 | Bus slots |        |       |       |

| VIPA 390-1AB60  | -         | 160mm  | 140mm | 10mm  |

| VIPA 390-1AE80  | -         | 482mm  | 466mm | 8,3mm |

| VIPA 390-1AF30  | -         | 530mm  | 500mm | 15mm  |

| VIPA 390-1AJ30  | -         | 830mm  | 800mm | 15mm  |

| VIPA 390-9BC00* | -         | 2000mm | -     | 15mm  |

| VIPA 391-1AF10  | 2         | 530mm  | 500mm | 15mm  |

| VIPA 391-1AF30  | 6         | 530mm  | 500mm | 15mm  |

| VIPA 391-1AF50  | 10        | 530mm  | 500mm | 15mm  |

|                 |           |        |       |       |

\* Unit pack 10 pieces

# HB140E - SM - Rev. 09/45

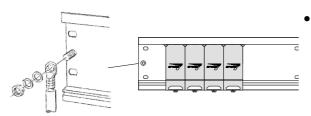

• Dismantle the according protection flaps of the SPEED-Bus plug-in locations with a screw driver (open and pull down).

For the SPEED-Bus is a parallel bus, not all SPEED-Bus plug-in locations must be used in series. Leave the protection flap installed at an unused SPEED-Bus plug-in location.

- At deployment of a DC 24V power supply, install it at the shown position at the profile rail at the left side of the SPEED-Bus and push it to the left to the isolation bolt of the profile rail.

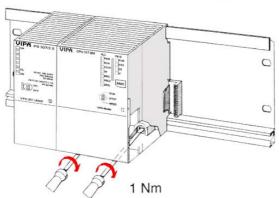

- Fix the power supply by screwing.

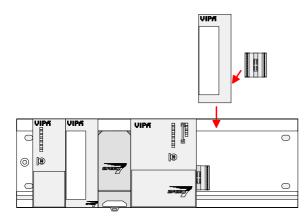

- To connect the SPEED-Bus modules, plug it between the triangular positioning helps to a plug-in location marked with "SLOT ..." and pull it down.

- Only the "SLOT1 DCDC" allows you to plug-in either a SPEED-Bus module or an additional power supply.

- Fix the modules by screwing.

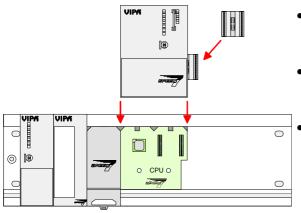

- To deploy the SPEED7-CPU exclusively at the SPEED-Bus, plug it between the triangular positioning helps to the plug-in location marked with "CPU SPEED7" and pull it down.

- Fix the CPU by screwing.

Please regard that not all CPU 31xS may be deployed at the SPEED-Bus!

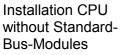

Installation CPU with Standard-Bus-Modules

- If also standard modules shall be plugged, take a bus coupler and click it at the CPU from behind like shown in the picture.

- Plug the CPU between the triangular positioning helps to the plug-in location marked with "CPU SPEED7" and pull it down.

- Fix the CPU by screwing.

• Repeat this procedure with the peripheral modules, by clicking a backplane bus coupler, stick the module right from the modules you've already fixed, click it downwards and connect it with the backplane bus coupler of the last module and bolt it.

# Danger!

- Before installing or overhauling the System, the power supplies must be disconnected from voltage (pull the plug or remove the fuse)!

- Installation and modifications only by properly trained personnel!

# Cabling

Overview

The power supplies and CPUs are exclusively delivered with CageClamp contacts. For the signal modules the front connectors are available from VIPA with screw contacts. In the following all connecting types of the power supplies, CPUs and input/output modules are described.

### Danger!

- Before installation or overhauling, the power supplies must be disconnected from voltage (pull the plug or remove the fuse)!

- Installation and modifications only by properly trained personnel!

### CageClamp technology (gray)

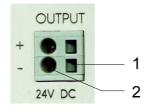

For the cabling of power supplies, bus couplers and parts of the CPU, gray connectors with CageClamp technology are used.

You may connect wires with a cross-section of 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup>. You can use flexible wires without end case as well as stiff wires.

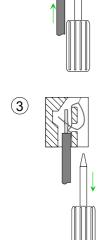

- [1] Rectangular opening for screwdriver

- [2] Round opening for wires

The picture on the left side shows the cabling step by step from top view.

- To conduct a wire you plug a fitting screwdriver obliquely into the rectangular opening like shown in the picture.

- To open the contact spring you have to push the screwdriver in the opposite direction and hold it.

- Insert the insulation striped wire into the round opening. You may use wires with a cross-section from 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup>.

- By removing the screwdriver the wire is connected safely with the plug connector via a spring.

### CageClamp technology (green)

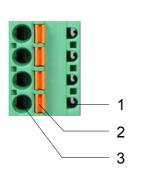

(1)

For the cabling of e.g. the power supply of a CPU, green plugs with CageClamp technology are deployed.

Here also you may connect wires with a cross-section of 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup>. You can use flexible wires without end case as well as stiff wires.

- [1] Test point for 2mm test tip

- [2] Locking (orange) for screwdriver

- [3] Round opening for wires

The picture on the left side shows the cabling step by step from top view.

- For cabling you push the locking vertical to the inside with a suiting screwdriver and hold the screwdriver in this position.

- Insert the insulation striped wire into the round opening. You may use wires with a cross-section from 0.08mm<sup>2</sup> to 2.5mm<sup>2</sup>.

- By removing the screwdriver the wire is connected safely with the plug connector via a spring.

### Note!

In opposite to the gray connection clamp from above, the green connection clamp is realized as plug that can be clipped off carefully even if it is still cabled.

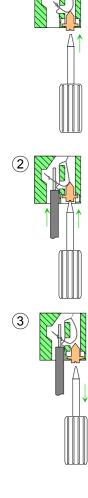

Front connectors of the in-/output modules In the following the cabling of the three variants of the front-facing connector is shown:

For the I/O modules the following plugs are available at VIPA:

continued ...

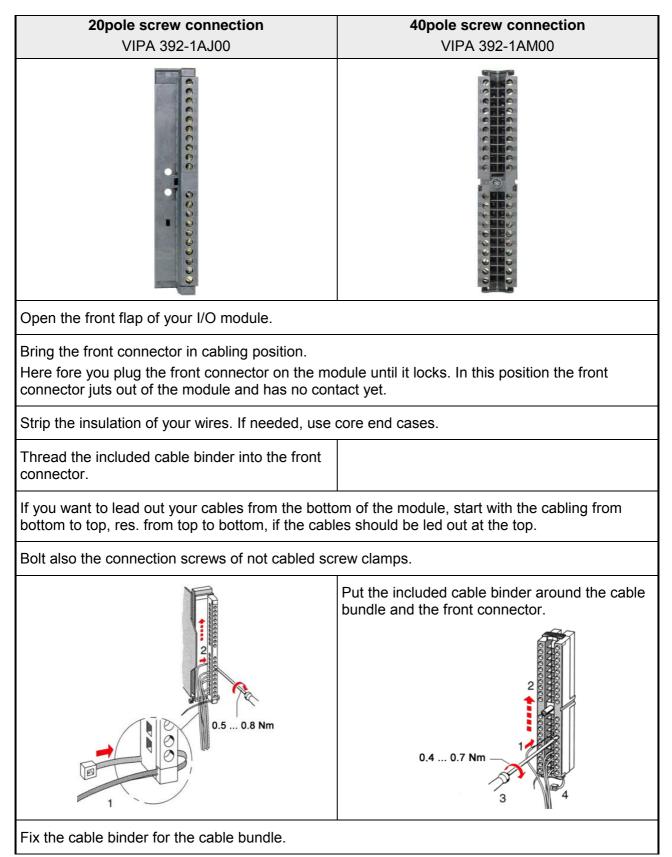

**20pole screw connection 40pole screw connection** VIPA 392-1AJ00 VIPA 392-1AM00 Push the release key at the front connector on Bolt the fixing screw of the front connector. the upper side of the module and at the same time push the front connector into the module until it locks. 2 11111111111 C CITERICI. 0.4 ... 0.7 Nm Now the front connector is electrically connected with your module. Close the front flap. Fill out the labeling strip to mark the single channels and push the strip into the front flap.

# **Installation Guidelines**

| General                            | The installation guidelines contain information about the interference free deployment of the System 300. There is the description of the ways, interference may occur in your control, how you can make sure the electromagnetic digestibility (EMC), and how you manage the isolation.                                                                                                                                                                                                                                                                    |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What means<br>EMC?                 | Electromagnetic digestibility (EMC) means the ability of an electrical device, to function error free in an electromagnetic environment without being interferenced res. without interferencing the environment.<br>All System 300 components are developed for the deployment in hard industrial environments and fulfill high demands on the EMC. Nevertheless you should project an EMC planning before installing the components and take conceivable interference causes into account.                                                                 |

| Possible<br>interference<br>causes | <ul> <li>Electromagnetic interferences may interfere your control via different ways:</li> <li>Fields</li> <li>I/O signal conductors</li> <li>Bus system</li> <li>Current supply</li> <li>Protected earth conductor</li> </ul> Depending on the spreading medium (lead bound or lead free) and the distance to the interference cause, interferences to your control occur by means of different coupling mechanisms. One differs: <ul> <li>galvanic coupling</li> <li>capacitive coupling</li> <li>inductive coupling</li> <li>radiant coupling</li> </ul> |

**Basic rules for** In the most times it is enough to take care of some elementary rules to guarantee the EMC. Please regard the following basic rules when installing your PLC.

- Take care of a correct area-wide grounding of the inactive metal parts when installing your components.

- Install a central connection between the ground and the protected earth conductor system.

- Connect all inactive metal extensive and impedance-low.

- Please try not to use aluminum parts. Aluminum is easily oxidizing and is therefore less suitable for grounding.

- When cabling, take care of the correct line routing.

- Organize your cabling in line groups (high voltage, current supply, signal and data lines).

- Always lay your high voltage lines and signal res. data lines in separate channels or bundles.

- Route the signal and data lines as near as possible beside ground areas (e.g. suspension bars, metal rails, tin cabinet).

- Proof the correct fixing of the lead isolation.

- Data lines must be laid isolated.

- Analog lines must be laid isolated. When transmitting signals with small amplitudes the one sided lying of the isolation may be favorable.

- Lay the line isolation extensively on an isolation/protected earth conductor rail directly after the cabinet entry and fix the isolation with cable clamps.

- Make sure that the isolation/protected earth conductor rail is connected impedance-low with the cabinet.

- Use metallic or metalized plug cases for isolated data lines.

- In special use cases you should appoint special EMC actions.

- Wire all inductivities with erase links that are not addressed by the modules.

- For lightening cabinets you should prefer incandescent lamps and avoid luminescent lamps.

- Create a homogeneous reference potential and ground all electrical operating supplies when possible.

- Please take care for the targeted employment of the grounding actions. The grounding of the PLC is a protection and functionality activity.

- Connect installation parts and cabinets with the System 300 in star topology with the isolation/protected earth conductor system. So you avoid ground loops.

- If potential differences between installation parts and cabinets occur, lay sufficiently dimensioned potential compensation lines.

Isolation of<br/>conductorsElectrical, magnetic and electromagnetic interference fields are weakened<br/>by means of an isolation, one talks of absorption.

Via the isolation rail, that is connected conductive with the rack, interference currents are shunt via cable isolation to the ground. Hereby you have to make sure, that the connection to the protected earth conductor is impedance-low, because otherwise the interference currents may appear as interference cause.

When isolating cables you have to regard the following:

- If possible, use only cables with isolation tangle.

- The hiding power of the isolation should be higher than 80%.

- Normally you should always lay the isolation of cables on both sides. Only by means of the both-sided connection of the isolation you achieve a high quality interference suppression in the higher frequency area.

Only as exception you may also lay the isolation one-sided. Then you only achieve the absorption of the lower frequencies. A one-sided isolation connection may be convenient, if:

- the conduction of a potential compensating line is not possible

- analog signals (some mV res. µA) are transferred

- foil isolations (static isolations) are used.

- With data lines always use metallic or metalized plugs for serial couplings. Fix the isolation of the data line at the plug rack. Do not lay the isolation on the PIN 1 of the plug bar!

- At stationary operation it is convenient to strip the insulated cable interruption free and lay it on the isolation/protected earth conductor line.

- To fix the isolation tangles use cable clamps out of metal. The clamps must clasp the isolation extensively and have well contact.

- Lay the isolation on an isolation rail directly after the entry of the cable in the cabinet. Lead the isolation further on to the System 300 module and **don't** lay it on there again!

# Please regard at installation!

At potential differences between the grounding points, there may be a compensation current via the isolation connected at both sides. Remedy: Potential compensation line

# Chapter 3 Digital I/O modules FAST - SPEED-Bus

Overview Content of this chapter is the structure and the functionality of the fast digital SPEED-Bus modules from VIPA. The modules can only be used at SPEED-Bus slots at the left side of the CPU.

# ContentTopicPageChapter 3Digital I/O modules FAST - SPEED-Bus3-1System overview3-2Security hint for DIO modules3-2Addressing at SPEED-Bus3-3Project engineering3-4321-1BH70 - DI 16xDC 24V3-8322-1BH70 - DO 16xDC 24V 0.5A3-19323-1BH70 - DIO 16xDC 24V 0.5A3-21

# System overview

I/O modules for SPEED-Bus

- SM 321S Fast Digital Input DI 16xDC 24V for SPEED-Bus

- SM 322S Fast Digital Output DO 16xDC 24V 0.5A for SPEED-Bus

- SM 323S Fast Digital Input/Output DIO 16xDC 24V 0.5A for SPEED-Bus

| Order data  | Туре               | Order No.      | Page |

|-------------|--------------------|----------------|------|

| I/O modules | DI 16xDC 24V       | VIPA 321-1BH70 | 3-8  |

|             | DO 16xDC 24V 0.5A  | VIPA 322-1BH70 | 3-19 |

|             | DIO 16xDC 24V 0.5A | VIPA 323-1BH70 | 3-21 |

# Security hint for DIO modules

# Attention!

Please regard that the voltage applied to an output channel must be  $\leq$  the voltage supply applied to L+.

Due to the parallel connection of in- and output channel per group, a set output channel may be supplied via an applied input signal. Thus, a set output remains active even at power-off of the voltage supply with the applied input signal. Non-observance may cause module demolition.

# Addressing at SPEED-Bus

| Overview                                         | To provide addresses                                                                         |                                                                                       |                                                                                       | •                                                                                            |                                                                                       |                                                                                          | eriphera                                                                    | al modules,                                                                                                                        | certain                          |

|--------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                  | peripheral                                                                                   | I/O ac                                                                                | dresse                                                                                | s during                                                                                     | boot p                                                                                | orocedure                                                                                | depend                                                                      | signs autom<br>ling on the<br>PEED-Bus.                                                                                            |                                  |

| Maximal pluggable<br>modules                     | parameter<br>standard b<br>CPs and l<br>bus are ta<br>For the p<br>line interfa<br>module IN | rized. A<br>ous and<br>DP mas<br>ken into<br>roject e<br>ace cor<br>A 360 f<br>may ex | t deplo<br>10 fur<br>sters the<br>the su<br>enginee<br>nection<br>from the<br>tend yo | yment o<br>ther mod<br>at are ad<br>m of 32<br>ring of 1<br>s. For the<br>hardwo<br>ur syste | f SPEE<br>dules at<br>dditiona<br>modules<br>more th<br>nis you<br>are cata<br>m with | ED7 CPUs<br>the SPE<br>lly virtual<br>s at the sl<br>an 8 mo<br>set in the<br>alog to sl | s up to<br>ED-Bus<br>configur<br>tandard l<br>dules yo<br>hardwa<br>ot 3 of | les per row r<br>32 modules<br>may be cor<br>red at the st<br>bus.<br>bu may use<br>re configura<br>your 1. prof<br>ils by startin | virtual<br>ator the<br>ile rail. |

| Define addresses<br>by hardware<br>configuration | peripheral<br>To define                                                                      | bytes<br>addres<br>ng the                                                             | or the p<br>ses, a ł<br>SPEE                                                          | rocess i<br>nardware<br>DBUS.G                                                               | mage.<br>e config<br>SSD ma                                                           | uration vi<br>ay be us                                                                   | ia a virtu<br>ed. For                                                       | accesses<br>al Profibus<br>this, click<br>ddress.                                                                                  | system                           |

| Automatic                                        | If you do i<br>comes inte                                                                    |                                                                                       |                                                                                       | a hardw                                                                                      | are con                                                                               | figuratior                                                                               | n, an aut                                                                   | tomatic addi                                                                                                                       | ressing                          |

| addressing                                       | At the au                                                                                    | tomatic<br>on with                                                                    | addres                                                                                |                                                                                              |                                                                                       |                                                                                          |                                                                             | depending<br>Ps with a d                                                                                                           |                                  |

|                                                  |                                                                                              | modu                                                                                  | le is st                                                                              |                                                                                              |                                                                                       |                                                                                          |                                                                             | om where a calculated w                                                                                                            |                                  |

|                                                  | DIOs:                                                                                        |                                                                                       |                                                                                       | Start ac                                                                                     | ldress =                                                                              | = 4·(slot - ´                                                                            | 101)+12                                                                     | 8                                                                                                                                  |                                  |

|                                                  | AIOs, FMs                                                                                    | s, CPs:                                                                               |                                                                                       | Start ac                                                                                     | ldress =                                                                              | = 256·(slo                                                                               | t -101)+:                                                                   | 2048                                                                                                                               |                                  |

|                                                  |                                                                                              |                                                                                       |                                                                                       | -                                                                                            | ,102                                                                                  | ,101                                                                                     | Slot                                                                        |                                                                                                                                    |                                  |

|                                                  |                                                                                              |                                                                                       | 104                                                                                   | 103                                                                                          | 102                                                                                   | 101                                                                                      |                                                                             |                                                                                                                                    |                                  |

|                                                  | f                                                                                            |                                                                                       |                                                                                       |                                                                                              |                                                                                       | Z                                                                                        |                                                                             | $\neq$                                                                                                                             |                                  |

|                                                  | Start                                                                                        |                                                                                       |                                                                                       |                                                                                              |                                                                                       | CPU 31xS                                                                                 |                                                                             |                                                                                                                                    |                                  |

|                                                  | Address<br>digital:<br>analog:                                                               | 140<br>2816                                                                           | 136<br>2560                                                                           | 132<br>2304                                                                                  | 128<br>2048                                                                           | CPU                                                                                      |                                                                             |                                                                                                                                    |                                  |

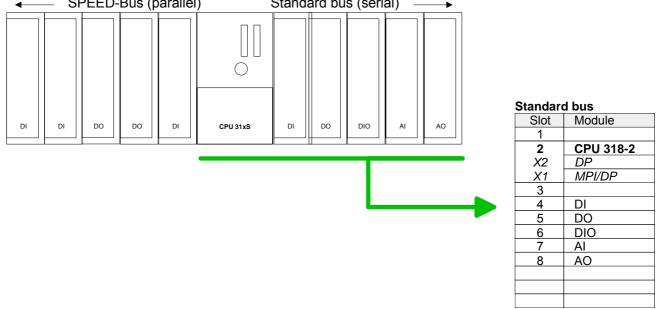

# **Project engineering**

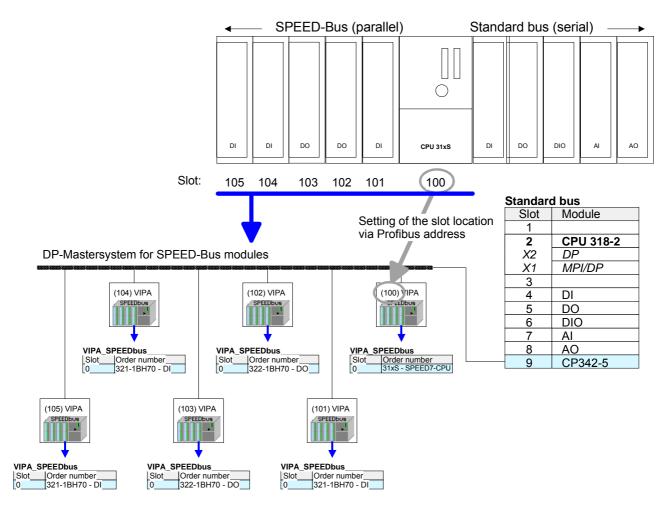

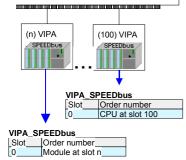

Overview Every module at the SPEED-Bus including the CPU has to be configured as single "VIPA\_SPEEDbus"-DP slave at a virtual DP master (342-5DA02 V5.0 from Siemens). For this you have to include the GSD speedbus.gsd. Every "VIPA SPEEDbus"-DP slave has exactly one slot for the project engineering where you must place the according SPEED-Bus module. The assignment of a SPEED-Bus slave to a SPEED-Bus slot number takes place via the Profibus address starting with 100.

### Fast introduction

For the employment of the I/O modules at the SPEED-Bus the inclusion via the GSD-file from VIPA in the hardware catalog is required.

To be compatible with the Siemens SIMATIC manager, you have to execute the following steps:

Standard bus

| Slot | Module                   |

|------|--------------------------|

| 1    |                          |

| 2    | CPU 318-2                |

| X2   | DP                       |

| X1   | MPI/DP                   |

| 3    |                          |

|      | nodules<br>ndard bus     |

| •••• | es. DP master<br>EED-Bus |

|      | 342-5DA02 V5.0           |

virtual DP master for CPU and all SPEED-Bus modules

•

- Start the hardware configurator from Siemens and include the speedbus.gsd for SPEED7 from VIPA.

- Configure CPU 318-2DP (6ES7 318-2AJ00-0AB0/V3.0) from Siemens.

- Starting with slot 4, place the System 300 modules in the plugged • sequence.

- Project engineering and connection of the SPEED-Bus-CPs res. –DP master at the standard bus as virtual CP 343-1 (343-1EX11) res. CP 342-5 (342-5DA02 V5.0)

- For the SPEED-Bus you always include, connect and parameterize to the operating mode DP master the DP master CP 342-5 (342-5DA02 V5.0) as last module. To this master system you assign every SPEED-Bus module as VIPA\_SPEEDbus slave. Here the Profibus address corresponds to the slot number beginning with 100 for the CPU. Place at slot 0 of every slave the assigned module and alter the parameters if needed.

# Preconditions

The hardware configurator is part of the Siemens SIMATIC manager. It serves for project engineering. The modules that may be configured here are listed in the hardware catalog.

For the employment of the System 300S modules at the SPEED-Bus you have to include the System 300S modules into the hardware catalog via the GSD-file speedbus.gsd from VIPA.

Note!

Chapter 3 Digital I/O modules FAST - SPEED-Bus

| 1                              | For the project engineering, a thorough knowledge of the Siemens<br>SIMATIC manager and the hardware configurator from Siemens is<br>required!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Include the<br>SPEED7-GSD-file | <ul> <li>Browse to www.vipa.de &gt; Service &gt; Download &gt; GSD- and EDS-Files &gt; Profibus and select the file <i>Cx000023_Vxxx</i>.</li> <li>Extract the file to your work directory. The SPEEDbus.gsd is stored in the directory System_300S.</li> <li>Start the hardware configurator from Siemens.</li> <li>Close all projects.</li> <li>Select <b>Options</b> &gt; <i>Install new GSD-file</i>.</li> <li>Change to the directory System_300S and select the <b>SPEEDBUS.GSD</b>. The modules of the System 300S from VIPA are now included in the hardware catalog under: <i>Profibus-DP / Additional field devices / I/O / VIPA_SPEEDbus</i>.</li> </ul> |

| Steps of project engineering   | The following text describes the approach of the project engineering in the hardware configurator from Siemens at an abstract sample.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

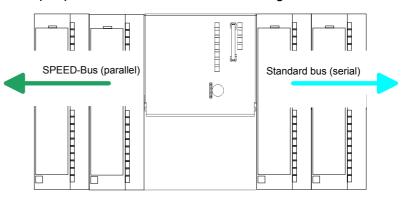

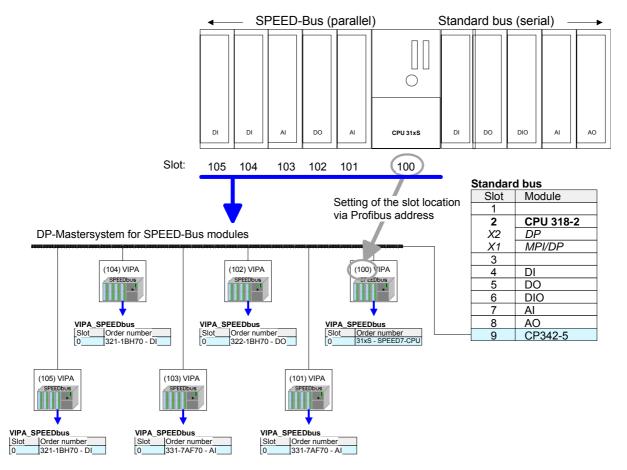

The project engineering is separated into following parts:

- Project engineering of the modules at the standard bus

- Project engineering of the SPEED-Bus modules in a virtual master system (speedbus.gsd required)

| -  | — SF | PEED- | Bus (p | arallel | ) :      | Standard bus (serial) |    |     |    |    |

|----|------|-------|--------|---------|----------|-----------------------|----|-----|----|----|

|    |      |       |        |         | 0        |                       |    |     |    |    |

| DI | DI   | DO    | DO     | DI      | CPU 31xS | DI                    | DO | DIO | AI | AO |

| Preconditions                         | For the employment of the System 300S modules at the SPEED-Bus you have to include the System 300S modules into the hardware catalog via the GSD-file speedbus.gsd from VIPA.                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project engineering of the modules at | The modules at the right side of the CPU at the standard bus are configured with the following approach:                                                                                            |

| the standard bus                      | <ul> <li>Start the hardware configurator from Siemens with a new project and<br/>insert a profile rail from the hardware catalog.</li> </ul>                                                        |

|                                       | <ul> <li>Place the following Siemens CPU at slot 2:<br/>CPU 318-2DP (6ES7 318-2AJ00-0AB0/V3.0)</li> </ul>                                                                                           |

|                                       | <ul> <li>Include your System 300V modules at the standard bus in the plugged<br/>sequence starting with slot 4.</li> </ul>                                                                          |

|                                       | <ul> <li>Parameterize the CPU res. the modules where appropriate. The<br/>parameter window opens by a double click on the according module.</li> </ul>                                              |

|                                       | <ul> <li>To extend the bus you may use the IM 360 from Siemens where you<br/>can connect up to 3 further extension racks via the IM 361. Bus<br/>extensions are always placed at slot 3.</li> </ul> |

|                                       | Save your project.                                                                                                                                                                                  |

| ← SPEED-Bus                           | (parallel) Standard bus (serial)►                                                                                                                                                                   |

### Note!

To extend the bus you may use the IM 360 from Siemens where you can connect up to 3 further extension racks via the IM 361. Bus extensions are always placed at slot 3.

Project engineering of all SPEED-Bus modules in a virtual master system The slot assignment of the SPEED-Bus modules and the parameterization of the in-/output periphery happens via a virtual Profibus DP master system. For this, place as last module a DP master (342-5DA02 V5.0) with master system.

For the employment of the System 300S modules at the SPEED-Bus the inclusion of the System 300S modules into the hardware catalog via the GSD-file speedbus.gsd from VIPA is required.

After the installation of the speedbus.gsd you may locate under *Profibus DP / Additional field devices / I/O / VIPA\_SPEEDbus* the DP slave system vipa\_speedbus.

Now include for the CPU and <u>every</u> module at the SPEED-Bus a slave system "vipa\_speedbus".

Set as Profibus address the slot no. (100...110) of the module and place the according module from the hardware catalog of VIPA\_speedbus to slot 0 of the slave system.

The according module is to be taken over from the HW Catalog of vipa\_speedbus to slot 0.

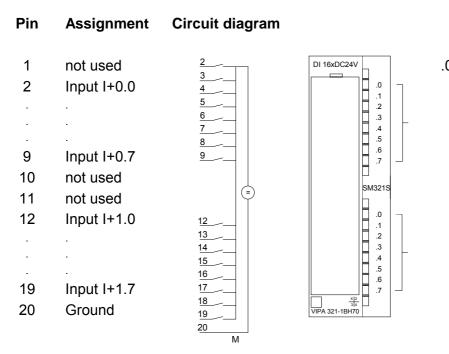

# 321-1BH70 - DI 16xDC 24V

| Order data | DI 16xDC 24V | VIPA 321-1BH70 |

|------------|--------------|----------------|

|------------|--------------|----------------|

**Description** The fast digital input module collects the binary control signals from the process level and transmits them galvanically separated to the superordinated bus system. It has 16 channels and their status is monitored via LEDs.

**Properties**

- 16 fast input channels, isolated to SPEED-Bus

- Extended parameterization possibility

- Nominal input voltage DC 24V

- Useable for switches and approximate switches

• Status monitoring of the channels via LEDs

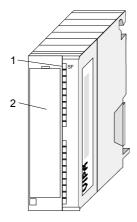

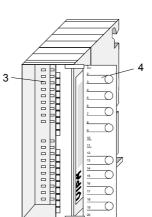

Construction

- [2] flap with labeling strip

- [3] contact bar

- [4] flap opened with inner label

Pin assignment Circuit diagram Status monitor

### LED Description

.0 ... .7 LEDs (green) I+0.0 to I+1.7 from ca. 15V on, the signal is recognized as "1" and the according LED is addressed

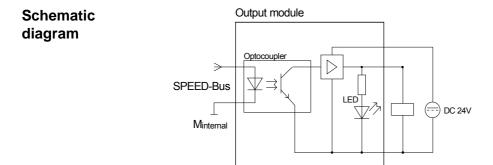

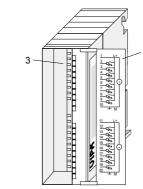

| Schematic      | Input Module       |

|----------------|--------------------|

| diagram        |                    |

| ←              | Optocoupler DC 24V |

| SPEED-Bus      |                    |

| ⊥<br>Minternal |                    |

|                |                    |

- **Parameterization** Depending on the project engineering, 2byte res. 48byte in the input range of the CPU where occupied by the module. You have the following opportunities for the project engineering: occupies the module. For project engineering there are the following possibilities:

- Project engineering as 321-1BH70 DI16xDC24V

| Range in PII: | 2byte |

|---------------|-------|

| Parameter:    | none  |

Project engineering as *DI16 Alarm/ETS* Range in PII: 48byte Parameter: 66byte (edge selection, time stamp, filter)

```

Project

engineering as

321-1BH70

DI16xDC24V

```

At this project engineering you have no parameterization options and your module occupies 2bytes in the input address range of the CPU. If no hardware project engineering is present, this operation mode is used

If no hardware project engineering is present, this operation mode is used as default. Here the module has a delay time of 6.12µs.

2

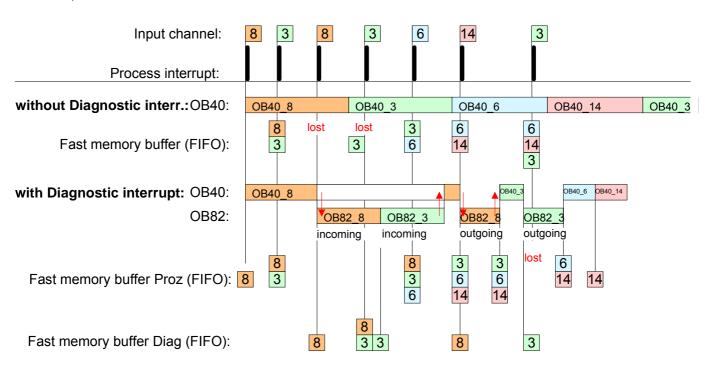

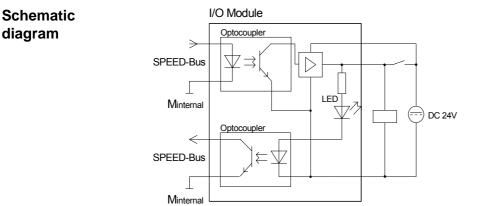

| Project<br>engineering as<br>DI16 Alarm/ETS   | configuration<br>parameterize<br>The following<br>Diagnostic<br>Edge sele<br>Time star | <ul> <li>If the module is defined as "DI16 Alarm/ETS" in the hardwar configuration, it occupies 48byte of the input range of the CPU and can b parameterized with 66byte of data.</li> <li>The following parameters are at your disposal:</li> <li>Diagnostic interrupt (global for all inputs)</li> <li>Edge selection (switchable process interrupt per channel)</li> <li>Time stamp (activation of a time stamp function per channel)</li> <li>Filter value (for grubby input signals per channel)</li> </ul> |  |  |  |  |  |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Structure of the parameter data               | the record se<br>alter parame                                                          | arameterization, a parameter area of 66byte is transferred in<br>ets 7Fh, 80h and 81h. Using the SFCs 55, 56 and 57 you may<br>ters and transfer them to the module during runtime.<br>ets have the following structure:                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| <b>Record set 7Fh</b><br>Diagnostic interrupt | diagnostic ir<br>another proc<br>The record s                                          | set activates res. de-activates the diagnostic function. A<br>nterrupt occurs when during a process interrupt execution<br>ess interrupt is initialized for the same event.<br>et has the following structure:                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                                               | Word                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                               | 0                                                                                      | Bit 15 0: Diagnostic interrupt<br>0000h = de-activated                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                                               | 0001h = activated                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

Bit 15 ... 0: reserved

## Record set 80h

Edge selection

Via this record set you may activate a process interrupt for I+0.0 ... I+1.7 and define for which edge of the input signal a process interrupt is thrown. The record set has the following structure:

| Duto |                                            |

|------|--------------------------------------------|

| Byte | Bit 7 0                                    |

| 0    | Bit 1 0: Edge selection I+0.0              |

|      | 00b = de-activated                         |

|      | 01b = Process interrupt at ascending edge  |

|      | 10b = Process interrupt at descending edge |

|      | 11b = Process interrupt at both edges      |

|      | Bit 7 2: reserved                          |

|      |                                            |

| 15   | Bit 1 0: Edge selection I+1.7              |

|      | 00b = de-activated                         |

|      | 01b = Process interrupt at ascending edge  |

|      | 10b = Process interrupt at descending edge |

|      | 11b = Process interrupt both edges         |

|      | Bit 7 2: reserved                          |

continued ...

#### ... continue record set 80h

| Record set 80h<br>ETS time stamp<br>(Byte 16 31) | Every SPEED-Bus module carries along a timer with a resolution of 1 $\mu$ s. The timer starts at boot-up of the CPU. Thus gives you a time base with an accuracy of $\pm 1\mu$ s at the SPEED-Bus. By parameterization of the ETS function ( <b>E</b> dge <b>T</b> ime <b>s</b> tamp) for an input, the current time value is entered in |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | the process image of the module at according edge. Thus allows you to                                                                                                                                                                                                                                                                    |

|                                                  | compare times of different input channels via your user application.                                                                                                                                                                                                                                                                     |

Via the parameter *Time stamp* you may activate the ETS system and define the edge of the input signal that initiates the process image entry of a time stamp. You have the following options:

- No time stamp

- Time stamp at ascending edge

- Time stamp at descending edge

- Time stamp at both edges

The allocation in the process image is illustrated at the following page.

### Note!

The stored times correspond the point in time when the signal has already passed the input filter of the module. To calculate the real time at the clamp, you have to subtract the delay time of  $1\mu s$  and the parameterized delay time defined under *Filter*.

| Byte | Bit 7 Bit 0                            |

|------|----------------------------------------|

| 16   | Bit 1,0: Time stamp channel 0 (I+0.0)  |

|      | 00 = no time stamp                     |

|      | 01 = Time stamp at ascending edge      |

|      | 10 = Time stamp at descending edge     |

|      | 11 = Time stamp at both edges          |

|      |                                        |

| 31   | Bit 1,0: Time stamp channel 15 (I+1.7) |

|      | 00 = no time stamp                     |

|      | 01 = Time stamp at ascending edge      |

|      | 10 = Time stamp at descending edge     |

|      | 11 = Time stamp at both edges          |

Record set 81hThis record set allows you to preset an input filter in steps of 5.12µs stepsInput filterfor I+0.0 ... I+1.7. By preceding a filter you define how long an input signal<br/>must be present before it is recognized as "1" signal. With the help of filters<br/>you may e.g. filter signal peaks at a blurred input signal.

The entry happens as a factor of  $5.12\mu$ s and is within the range 1 ... 31250 i.e.  $5.12\mu$ s ... 160ms. The record set has the following structure:

| Word |                              |

|------|------------------------------|

| 0    | Input filter I+0.0 in 5.12µs |

|      |                              |

| 30   | Input filter I+1.7 in 5.12µs |

**48bytes in the** The module occupies 48byte in the input address range of the CPU that have the following meaning:

| Byte     | Bit 7 Bit 0                                                          |

|----------|----------------------------------------------------------------------|

| 0        | State of the channels (1 = set, 0 = not set)                         |

|          | Bit 0: Status I+0.0                                                  |

|          |                                                                      |

| 1        | Bit 7: Status I+0.7                                                  |

|          | State of the channels (1 = set, 0 = not set)<br>Bit 8: Status I+1.0  |

|          |                                                                      |

|          | Bit 15: Status I+1.7                                                 |

| 2 3      | reserved                                                             |

| 4        | 1. edge evaluation (1=edge detected, 0=no edge detected)             |

|          | Here the last presence of an edge since the last read access to      |

|          | the register is stored. After a read access to this register (in the |

|          | module) it is set back.<br>Bit 0: Status I+0.0                       |

|          |                                                                      |

|          | Bit 7: Status I+0.7                                                  |

| 5        | Edge evaluation                                                      |

|          | Bit 0: Status I+1.0                                                  |

|          |                                                                      |

| 6 7      | Bit 7: Status I+1.7                                                  |